2025-03-03 00:14:47

LPDDR4在片選和功耗優(yōu)化方面提供了一些特性和模式,以提高能效和降低功耗。以下是一些相關(guān)的特性:片選(ChipSelect)功能:LPDDR4支持片選功能,可以選擇性地特定的存儲芯片,而不是全部芯片都處于活動狀態(tài)。這使得系統(tǒng)可以根據(jù)需求來選擇使用和存儲芯片,從而節(jié)省功耗。命令時鐘暫停(CKEPin):LPDDR4通過命令時鐘暫停(CKE)引腳來控制芯片的活躍狀態(tài)。當命令時鐘被暫停,存儲芯片進入休眠狀態(tài),此時芯片的功耗較低。在需要時,可以恢復命令時鐘以喚醒芯片。部分功耗自動化(PartialArraySelfRefresh,PASR):LPDDR4引入了部分功耗自動化機制,允許系統(tǒng)選擇性地將存儲芯片的一部分進入自刷新狀態(tài),以減少存儲器的功耗。只有需要的存儲區(qū)域會繼續(xù)保持活躍狀態(tài),其他區(qū)域則進入低功耗狀態(tài)。數(shù)據(jù)回顧(DataReamp):LPDDR4支持數(shù)據(jù)回顧功能,即通過在時間窗口內(nèi)重新讀取數(shù)據(jù)來減少功耗和延遲。這種技術(shù)可以避免頻繁地從存儲器中讀取數(shù)據(jù),從而節(jié)省功耗。LPDDR4的數(shù)據(jù)保護機制是什么?如何防止數(shù)據(jù)丟失或損壞?龍華區(qū)解決方案LPDDR4信號完整性測試

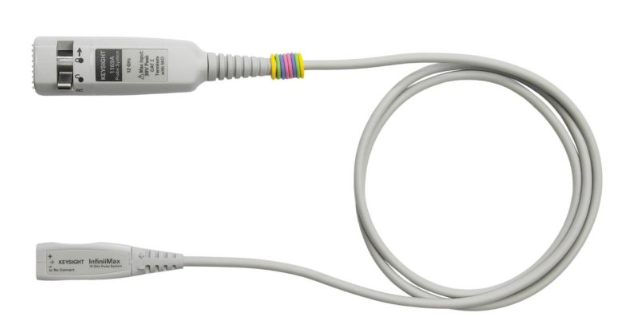

LPDDR4的故障診斷和調(diào)試工具可以幫助開發(fā)人員進行性能分析、故障排查和系統(tǒng)優(yōu)化。以下是一些常用的LPDDR4故障診斷和調(diào)試工具:信號分析儀(Oscilloscope):信號分析儀可以實時監(jiān)測和分析LPDDR4總線上的時序波形、電壓波形和信號完整性。通過觀察和分析波形,可以檢測和診斷信號問題,如時鐘偏移、噪音干擾等。邏輯分析儀(LogicAnalyzer):邏輯分析儀可以捕捉和分析LPDDR4控制器和存儲芯片之間的通信和數(shù)據(jù)交互過程。它可以幫助診斷和調(diào)試命令和數(shù)據(jù)傳輸?shù)膯栴},如錯誤指令、地址錯誤等。頻譜分析儀(SpectrumAnalyzer):頻譜分析儀可以檢測和分析LPDDR4總線上的信號頻譜分布和頻率響應。它可幫助發(fā)現(xiàn)和解決頻率干擾、諧波等問題,以提高信號質(zhì)量和系統(tǒng)性能。仿真工具(SimulationTool):仿真工具可模擬LPDDR4系統(tǒng)的行為和性能,幫助研發(fā)人員評估和分析不同的系統(tǒng)配置和操作。通過仿真,可以預測和優(yōu)化LPDDR4性能,驗證設(shè)計和調(diào)試系統(tǒng)。調(diào)試器(Debugger):調(diào)試器可以與LPDDR4控制器、存儲芯片和處理器進行通信,并提供實時的調(diào)試和追蹤功能。它可以幫助研發(fā)人員監(jiān)視和控制LPDDR4的狀態(tài)、執(zhí)行調(diào)試命令和觀察內(nèi)部數(shù)據(jù),以解決軟件和硬件間的問題寶安區(qū)儀器儀表測試LPDDR4信號完整性測試LPDDR4與LPDDR3相比有哪些改進和優(yōu)勢?

LPDDR4的物理接口標準是由JEDEC(電子行業(yè)協(xié)會聯(lián)合開發(fā)委員會)定義的。LPDDR4使用64位總線,采用不同的頻率和傳輸速率。LPDDR4的物理接口與其他接口之間的兼容性是依據(jù)各個接口的時序和電信號條件來確定的。下面是一些與LPDDR4接口兼容的標準:LPDDR3:LPDDR4與之前的LPDDR3接口具有一定程度的兼容性,包括數(shù)據(jù)總線寬度、信號電平等。但是,LPDDR4的時序規(guī)范和功能要求有所不同,因此在使用過程中可能需要考慮兼容性問題。DDR4:盡管LPDDR4和DDR4都是面向不同領(lǐng)域的存儲技術(shù),但兩者的物理接口在電氣特性上是不兼容的。這主要是因為LPDDR4和DDR4有不同的供電電壓標準和功耗要求。需要注意的是,即使在物理接口上存在一定的兼容性,但仍然需要確保使用相同接口的設(shè)備或芯片能夠正確匹配時序和功能設(shè)置,以保證互操作性和穩(wěn)定的數(shù)據(jù)傳輸。

LPDDR4采用的數(shù)據(jù)傳輸模式是雙數(shù)據(jù)速率(DoubleDataRate,DDR)模式。DDR模式利用上升沿和下降沿兩個時鐘信號的變化來傳輸數(shù)據(jù),實現(xiàn)了在每個時鐘周期內(nèi)傳輸兩個數(shù)據(jù)位,從而提高數(shù)據(jù)傳輸效率。關(guān)于數(shù)據(jù)交錯方式,LPDDR4支持以下兩種數(shù)據(jù)交錯模式:Byte-LevelInterleaving(BLI):在BLI模式下,數(shù)據(jù)被分為多個字節(jié),然后按照字節(jié)進行交錯排列和傳輸。每個時鐘周期,一個通道(通常是64位)的字節(jié)數(shù)據(jù)被傳輸?shù)絻?nèi)存總線上。這種交錯方式能夠提供更高的帶寬和數(shù)據(jù)吞吐量,適用于需要較大帶寬的應用場景。LPDDR4是否支持ECC(錯誤檢測與糾正)功能?

實現(xiàn)并行存取的關(guān)鍵是控制器和存儲芯片之間的協(xié)議和時序控制。控制器需要能夠識別和管理不同通道之間的地址和數(shù)據(jù),確保正確的通道選擇和數(shù)據(jù)流。同時,存儲芯片需要能夠接收和處理來自多個通道的讀寫請求,并通過相應的通道進行數(shù)據(jù)傳輸。需要注意的是,具體應用中實現(xiàn)并行存取需要硬件和軟件的支持。系統(tǒng)設(shè)計和配置需要根據(jù)LPDDR4的規(guī)范、技術(shù)要求以及所使用的芯片組和控制器來確定。同時,開發(fā)人員還需要根據(jù)實際需求進行性能調(diào)優(yōu)和測試,以確保并行存取的有效性和穩(wěn)定性。LPDDR4是否支持片選和功耗優(yōu)化模式?鹽田區(qū)數(shù)字信號LPDDR4信號完整性測試

LPDDR4的時鐘和時序要求是由JEDEC定義并規(guī)范的。龍華區(qū)解決方案LPDDR4信號完整性測試

LPDDR4是一種低功耗的存儲器標準,具有以下功耗特性:低靜態(tài)功耗:LPDDR4在閑置或待機狀態(tài)下的靜態(tài)功耗較低,可以節(jié)省電能。這對于移動設(shè)備等需要長時間保持待機狀態(tài)的場景非常重要。動態(tài)功耗優(yōu)化:LPDDR4設(shè)計了多種動態(tài)功耗優(yōu)化技術(shù),例如自適應溫度感知預充電、寫執(zhí)行時序調(diào)整以及智能供電管理等。這些技術(shù)可以根據(jù)實際工作負載和需求動態(tài)調(diào)整功耗,提供更高的能效。低電壓操作:LPDDR4采用較低的工作電壓(通常為1.1V或1.2V),相比于以往的存儲器標準,降低了能耗。同時也使得LPDDR4對電池供電產(chǎn)品更加節(jié)能,延長了設(shè)備的續(xù)航時間。在不同的工作負載下,LPDDR4的能耗會有所變化。一般來說,在高負載情況下,如繁重的多任務處理或大規(guī)模數(shù)據(jù)傳輸,LPDDR4的能耗會相對較高。而在輕負載或空閑狀態(tài)下,能耗會較低。需要注意的是,具體的能耗變化會受到許多因素的影響,包括芯片設(shè)計、應用需求和電源管理等。此外,動態(tài)功耗優(yōu)化技術(shù)也可以根據(jù)實際需求來調(diào)整功耗水平。龍華區(qū)解決方案LPDDR4信號完整性測試